The recently released Intel® Atom™ architecture utilized the same basic data flows as the Intel® Core™ 2 Duo architecture, but instead of just the MCH and ICH, the Intel® Atom™ processor can connect to a System Controller Hub (SCH). The SCH integrates most of the MCH and ICH functionality into one device that optimizes the interfaces for ultra low power applications. The target markets for the SCH do not require the same number of ports on each interface that the ICH can provide. For designs based on the Intel® Atom™ processor, there is also a version of the MCH/ICH that can work with the Intel® Atom™ CPU to provide the large quantity of I/O ports, if it is needed. The SCH provides a similar power management role as the ICH and should be powered first. The basic components that make up the Intel® architecture system are the CPU, memory controller, and I/O controller. Supporting these components are non-volatile memory, power supplies, and some glue logic.

The components shown are:

• IOH – I/O Hub

• ICH – I/O Controller Hub

• SCH – System Controller Hub

• MCH – Memory Controller Hub

The interfaces shown are:

The Intel® Atom™ processor design is optimized for very low power consumption. The voltage levels are lower and the speed of the FSB is lower than the Intel® Core™ 2 Duo. The lower speed FSB allows CMOS drivers to be used which draw less power than the GTL drivers. Another capability of the Intel® Atom™ CPU is to dynamically reduce on chip cache size to save power.

The SCH has many advanced power management capabilities to enable the lowest possible platform power consumption

Memory Controller

The central hub for the data traffic in an Intel® architecture system is the Memory Controller Hub (MCH). Until the new Intel® Atom™ and Intel® Core™ i7 architectures were developed, the MCH had been a discrete component. The Intel® Core™ 2 Duo architecture uses a discrete MCH which will be described first. shows the MCH for a system featuring the Intel® Core™ 2 Duo processor. The MCH facilitates the transfer of data to and from all the interfaces. When the BIOS configures the MCH, it defines the base address locations for all the interfaces. The BIOS relays the configuration information to the operating system so it knows the capabilities and locations of the hardware that is in its system.

There are many different models of MCH currently offered by Intel. The feature differences between MCH’s include the number and type of memory channels, the number of PCIe* lanes supported, internal 2D/3D graphics, single or multiple CPU support (uni-processor (UP) or dual-processor (DP) or multi-processor (MP)). Intel validates specific CPU’s with specific MCH’s to provide a well balanced platform. Not all CPU FSB speeds are compatible with all MCH.

fig:MCH

The CPU connects to the MCH through the FSB which was described earlier. The FSB unit in the MCH is responsible for the CPU cache coherency. If data at the address requested is not in the CPU cache, or the data in memory is newer, the memory controller is told to retrieve the data at that address. Data transfers between the CPU and memory are always 64 bits, the full width of the L2 cache on the CPU. If only a byte of data is requested, the full 64 bits is retrieved but the CPU will only use 8 of those bits. The memory controller is configurable by the BIOS to support multiple speeds and sizes of memory. The refreshing of the DRAM is handled by the memory controller after it’s initially configured. The specific type, size, and speed of memory that is supported, varies by the model of MCH. The Direct Media Interface (DMI) interface in the MCH is a dedicated serial link to the I/O Controller Hub (ICH). The DMI link is actually four serial links, with dedicated transmit and receive pins. These serial links are referred to as “lanes” and all use differential signaling. So the DMI is 4 lanes x Transmit and Receive (2) x differential signaling (2) = 32 pins. The DMI usage will be described in a separate section.

DMI supports signaling of 2.5GT/s. The PCI Express* (PCIe*) interface is the highest bandwidth I/O interface in the IA system. The number of PCIe lanes can vary depending on the MCH used, but will usually be in multiples of 8. A common width for PCIe is 16 lanes as this is the maximum width for discrete PCIe graphics cards. The PCIe interface uses the same differential signaling that the DMI does, but PCIe supports higher transfer rates. The original PCIe specification states data rates of 2.5 GB/s per lane (this what DMI uses). The second generation of PCIe is now available and doubles the data rate to 5Gb/s. Many of the MCH versions also have internal graphics controllers. The details of the graphics controllers won’t be covered in this document, but the basic capabilities are 2D and 3D acceleration. The type of display interfaces directly supported by MCH’s varies by the model.

I/O Controller

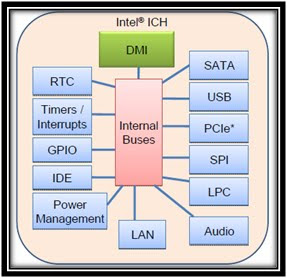

The I/O Controller Hub (ICH) provides extensive I/O support, support for legacy peripherals dating back to the 1980s, and integrates support for key platform management functions such as power sequencing and ACPI power management, fan speed control, and reset timing. It will be seen that these later functions are critical to system operation and often overlooked by designers.

fig: ICH

As the ICH is used to control the reset sequence, and often power sequencingof the other system components, it has power supplies which are required to turn on before the rest of the system. Also, the Real Time Clock (RTC) needs to have a 32.768KHz oscillator running before to properly sequence. The ICH communicates with the IOH/MCH during reset and power cycling events to try to make these events “safer”. For example, a warning message will be sent over DMI before a reset to allow SMBUS or memory transactions to complete before the reset.

Modern I/O interfaces

The ICH acts a bridge or controller for a variety of industry standard interfaces allowing the system designer to choose from a wide range of peripherals.

• PCI interface operates at 33MHz and allowing for a number of external bus masters. The ICH acts as the central arbiter and root of the PCI bus.

• PCI Express* root port controllers. The number of ports varies with the product but is generally in the range of 1 to 4. Link widths of x1 x4 are support at speeds of 2.5GB/s.

• Serial ATA (SATA) controllers supporting both legacy operation using I/O space and the Advanced Host Controller Interface (AHCI) using memory mapped I/O as well as allowing advanced features such has hot-plug and native command queuing. SATA II supports data

rates of 1.5Gb/s and 3Gb/s.

• Integrated Drive Electronics (IDE) controllers are also used to control hard disc drives, and CD/DVD drives. They have been replaced in some platforms by the newer SATA interface since it offers better performance over a smaller interface.

• Universal Serial Bus (USB) supporting High Speed USB 2.0 (480 Mb/s) operation as well as full-speed (12 Mb/s) and low-speed signaling.

• General Purpose I/O (GPIO) pins for system customization. Many pins can also be configured to cause interrupts or wake events.

• System Management Bus (SMBus 2.0) The SMBus Host interfaces allows the processor to communicate with SMBus slaves. This interface is also compatible with most I2C devices. Slave functionality, including the Host Notify protocol is implemented. Hence, the host controller supports eight command protocols of the SMBus interface (see System

Management Bus (SMBus) Specification, Version 2.0): Quick Command, Send Byte, Receive Byte, Write Byte/Word, Read Byte/Word, Process Call, Block Read/Write, and Host Notify.

• Serial Peripheral Interface (SPI) is used to interface to BIOS flash devices which contain the boot firmware and initialization code. Up to 2 SPI flash devices operating at 33 MHz can be connected. Note that the flash devices connected to the LPC interface are quickly becoming obsolete and SPI is expected to be standard interface for BIOS flash in the future. The ICH is always a master on the SPI interface.

• Low Pin Count Interface (LPC) This interface replaces the ISA bus originally developed by IBM in the early 1980s, but uses only 7 signals plus a clock. It can be used to connect to a variety low speed devices that don’t require the bandwidth of PCI or PCI Express*. This interface is typically used to interface with Super I/O devices which contain many interfaces such as floppy driver controller, PS2 keyboard/mouse controls and serial ports.

• JTAG Boundary Scan allows testing of PCB board after assembly.

Support peripherals

The ICH integrates numerous support peripherals that replace many external components.

• Real Time Clock (RTC): The RTC is compatible with the Motorola MC146818A*. It contains 256 bytes of RAM that can be maintained with a 3V battery. 242 bytes are available for use while the remaining is dedicated to the clock function. The RTC supports generating wake events up to 30 days in the future. An external 32.768 KHz crystal is required for operation.

• High Precision Event Timers These are high resolution timers which can be used to generate periodic or one-shot interrupts. There are 8 comparators which share a common counter that is clocked from a MHz source.

• Advanced Programmable Interrupt Controller (APIC) is a more modern interrupt controller than the 82C59 (see below). It supports multiprocessor/multi core interrupt management and allows interrupts to be directed to a specific processor. The I/O APIC in the ICH can support up to 24 interrupt vectors and can work in conjunction with I/O APICs in other devices (such as the IOH) to help eliminate the need for multiple device to share interrupts. – flat panel display interface.

The I/O and peripheral interface differences between the ICH and SCH are listed below.

• SDIO Secure Digital Input / Output – Usually used for media cards.

• MMC Multi-Media Card – Usually used for media cards.

• SDVO Serial Digital Video Out – display interface.

• LVDS Low Voltage Digital Signaling – flat panel display interface.

There can also moreover some precise strategies in keeping with location or knowledge. Your competencies depend on how you bought this opportunity and wherein you have professional. non-public or expert training may distinguish between each other. idea over right here are beneficial for distinct guys additionally because it did for me. ti 84 plus ce games

ReplyDelete